# PDP-5 INTERRUPT SYSTEM PROGRAMMER'S GUIDE

Gary D. Hornbuckle

University of California, Berkeley

Document No. 30.60.15.

Issued May 7, 1965

Revised December 4, 1965

Contract SD-185

Office of Secretary of Defense

Advanced Research Projects Agency

Washington 25, D.C.

#### 1.0 Introduction

The PDP-5 Interrupt System has been modified to provide automatic encoding of the device flags which cause interrupts.

Upon receiving an interrupt, reading one word into the Accumulator, and executing that word as an instruction, a branch to one of 16 trap routines located anywhere in PDP-5 memory occurs.

In addition, there are instructions for independently arming and disarming individual interrupts.

At present, interrupts exist for the following:

| (1) | 93 <b>0/PDP-</b> 5 | Link | Receive  |

|-----|--------------------|------|----------|

| 1 1 | 7 10/ 1101 - 1     |      | TICCETAC |

\* To be added soon.

<sup>(6)</sup> Tablet Pen-up

<sup>(7)</sup> Tablet Match

<sup>(8)</sup> Display GØ

<sup>[(9)</sup> Display Keyboard]\*

#### 2.0 General Operation

Each interrupt (except GO) has two memory elements associated with it: (a) a flag which when true causes the interrupt and which must be reset by program control, and (b) an arm/disarm bit which must be true (armed) in order for the interrupt to occur regardless of the state of the flag bit. In some cases (teleprinter, keyboard, 930 Link) the flag bit may be sensed with skip instructions.

Whenever an interrupt flag comes true for an <u>armed</u> flag, and provided an IØN has been executed since the previous interrupt or since the machine was last halted, the contents of the P-counter are stored in memory location 1 and the instruction in location 2 is executed. Normally the contents of the Interrupt Counter are then read into the AC, stored in memory, and then executed to provide an indirect jump through a transfer vector to the particular interrupt processing routine involved. Within the interrupt routine the flag is turned off and the state of the arm bit changed if necessary. A general "return" routine would next execute an IØN and continue processing the interrupted task.

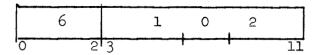

#### 3.0 <u>Interrupt Counter</u>, <u>IC</u>

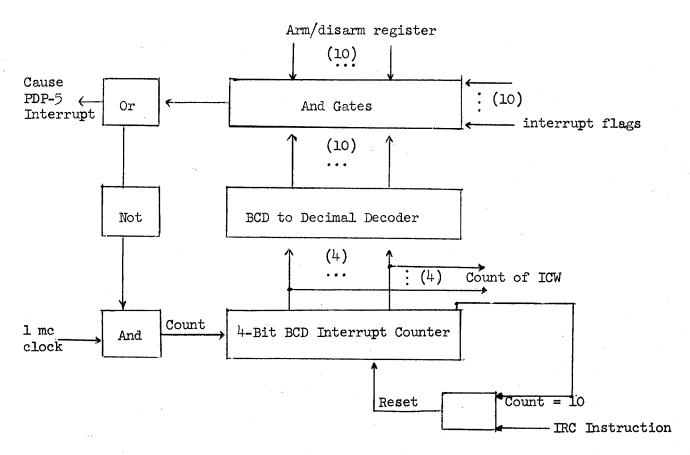

The IC is derived from a scanner (See Figure 1.) which scans the interrupt flags, one every microsecond; the current set of flags is scanned every 10 usec. When an armed interrupt occurs, the scanner stops when the count representing the interrupt is reached. The scanner is then released whenever the interrupt flag is turned off or the counter reset. Since execution of IRC resets the counter, some "hardware priority" control is provided by executing IRC just prior to enabling interrupts. If an interrupt with higher C ("higher priority") has occurred, it will be serviced next.

Figure 1: PDP-5 Interrupt Scanner Logic

## 4.0 <u>Enable/Disable Interrupts</u>

The standard PDP-5 facility for controlling all interrupts simultaneously has not been modified. The following IØT's are for this purpose.

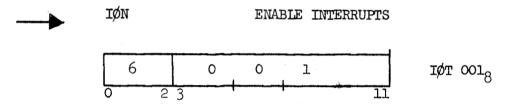

Turn interrupt control on. The instruction following ION is privileged; i.e., it will be executed before the next interrupt occurs.

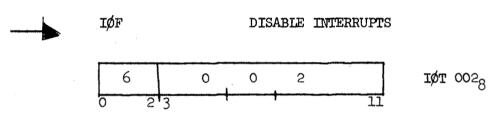

Turn interrupt control off. The equivalent of this instruction is executed at the time each interrupt occurs to prevent multiple interrupts.

### 4.1. Arm/Disarm Interrupts

Two instructions are provided to prevent (disarm) or allow (arm) the occurrence of each interrupt individually.

At the time of execution, certain bits of the accumulator are associated with each interrupt. See Part 7.0.

ARM

ARM INTERRUPTS

IØT 101<sub>8</sub>

Arm those interrupts whose associated accumulator bit is ON. Other interrupts are unaffected.

DARM

DISARM INTERRUPTS

IØT 1028

Disarm those interrupts whose associated accumulator bit is ON. Other interrupts are unaffected.

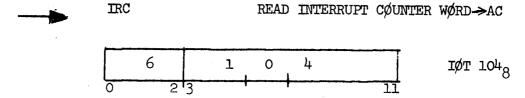

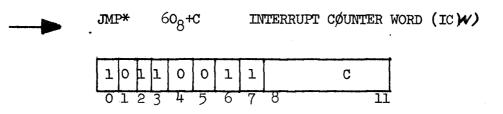

### 5.0. Interrupt Counter Word, ICW

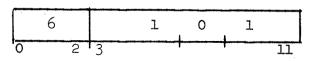

The word read into the accumulator is called the Interrupt Counter Word and is read with the following IØT instruction:

The contents of the accumulator will be OR'd with the contents of the Interrupt Counter Word which has the following bit pattern:

where C represents which of 16 interrupts occurred. If the IC is executed, a branch will occur to one of 16 locations whose address is specified by the contents of locations 60-77 of page 0. The current assignments are given in part 7.0.

The following table contains all the detailed information necessary for operation of the PDP-5 interrupt system.

| Interrupt               | ARM<br>Accumula<br>Contents | ator | IC<br>Contents | Page 0<br>Location | Flag<br>Reset<br>Instruction   | Flag<br>Sense<br>Skip if True |

|-------------------------|-----------------------------|------|----------------|--------------------|--------------------------------|-------------------------------|

| 930 Link<br>Transmit    | 1 <sub>8</sub>              | 11   | 17             | 77                 | 6212<br>6211                   | 6211**                        |

| 930 Link<br>Receive     | 28                          | 10   | 16             | 76                 | 62 <b>0</b> 1<br>62 <b>12</b>  | 6201                          |

| Tablet/Display<br>Match | <sup>4</sup> 8              | 9    | 15             | 75                 | 611 <sup>4</sup><br>(GØ buttor | <br>1)                        |

| Tablet<br>Pen-down      | 108                         | 8    | 14             | 74                 | 6111<br>6112<br>62 <b>12</b>   |                               |

| Tablet<br>Pen-up        | 20 <sub>8</sub>             | 7    | 13             | 73                 | 620 <b>2</b><br>621 <b>2</b>   |                               |

| PDP-5<br>Keyboard       | 40 <sub>8</sub>             | 6    | 12             | 72                 | 6032                           | 6031                          |

| PDP-5<br>Teleprinter    | 1008                        | 5    | 11             | 71                 | 6042                           | 6041                          |

| Display<br>GØ           | Go is<br>always<br>armed    |      | 10             | 70                 | 621 <b>2</b>                   |                               |

| Display<br>Keyboard*    | 200 <sub>8</sub>            | 4    | 07             | 67 <b>***</b>      | <b>6222</b><br>6212            | ·                             |

## Special Instructions

| IØT | 001 | Enable   |

|-----|-----|----------|

| IØT | 002 | Disable  |

| IØT | 101 | Arm**    |

| IØT | 102 | Disarm** |

| ÍÓT | 104 | Read IC  |

<sup>\*</sup> To be added soon.

<sup>\*\*</sup> Also clears accumulator

<sup>\*\*\*</sup> Locations 60-66 are currently unassigned and won't occur

## 7.0. PDP-5 System Program - Interrupt Control

A sample PDP-5 interrupt control program is given below. The individual interrupt routines are responsible for preserving the state of the machine, turning off the flag, and enabling traps when they have reached a state in which they themselves can be reentered.

| Location (O | ctal) Instruction | Comments                                    |

|-------------|-------------------|---------------------------------------------|

| 0           |                   | Program Counter                             |

| 1           | on on on to       | Interrupt Store Location                    |

| 2           | DCA ACC           | Start of Interrupt Control Routine, Save AC |

| 3           | IRC               | Read Interrupt Counter Word                 |

| 4           | DCA .+1           | Execute It                                  |

| 5           | JMP* 60+C         |                                             |

| ACC         |                   | Accumulator Saved                           |

| Return RET  | CLA               | For Return From Interrupt Routines          |

|             | TAD ACC           | Restore AC                                  |

|             | IØN               | Re-Enable Interrupts                        |

|             | JMP* 1            | Return to Last Routine in Control           |

| 67          | DKBD              | Display Keyboard                            |

| 70          | GØ                | Display GØ                                  |

| 71          | TPR               | PDP-5 Teleprinter                           |

| 72          | KBD               | PDP-5 Keyboard                              |

| 73          | PU                | Tablet Pen-up                               |

| 74          | PD                | Tablet Pen-down                             |

| 75          | LT                | 930 Link Transmit                           |

| Location (Octal) | Instruction | Comments                           |

|------------------|-------------|------------------------------------|

| 76               | LR          | 930 Link Receive                   |

| 77               | MAT         | Locations of Interrupt<br>Routines |

The preceding program costs 66 usec. to get to an Interrupt Routine, and 60 usec. to return to the interrupted task, or 126 usec. overhead.